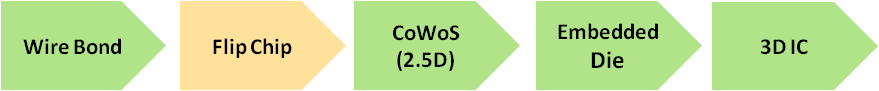

近年封装技术不断演进,从Wire Bond 到3D IC,IC Bump 的微缩将成为不可避免的趋势。封装技术的精进,也间接影响以下技术的发展。

Ø IC尺寸日益缩小

Ø Bump Pitch 不断微缩

Ø IC复杂度提升

Ø 信号传输速度增加

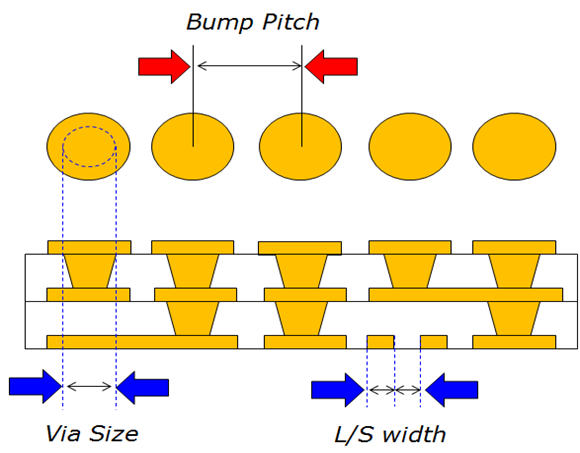

当IC Bump微缩将面临两种技术的挑战,一则为微小孔径,另一者为微细线宽/间距,

目前晶测的技术已可达微间距20um,细线路20um。

微小孔径

以微影制程取代机械加工制程,结合薄膜技术,制作微小的孔径,但也因孔径缩小易造成可靠度的问题,

故晶测以2.5D取代2D结构,并建立该结构及制程的相关专利。

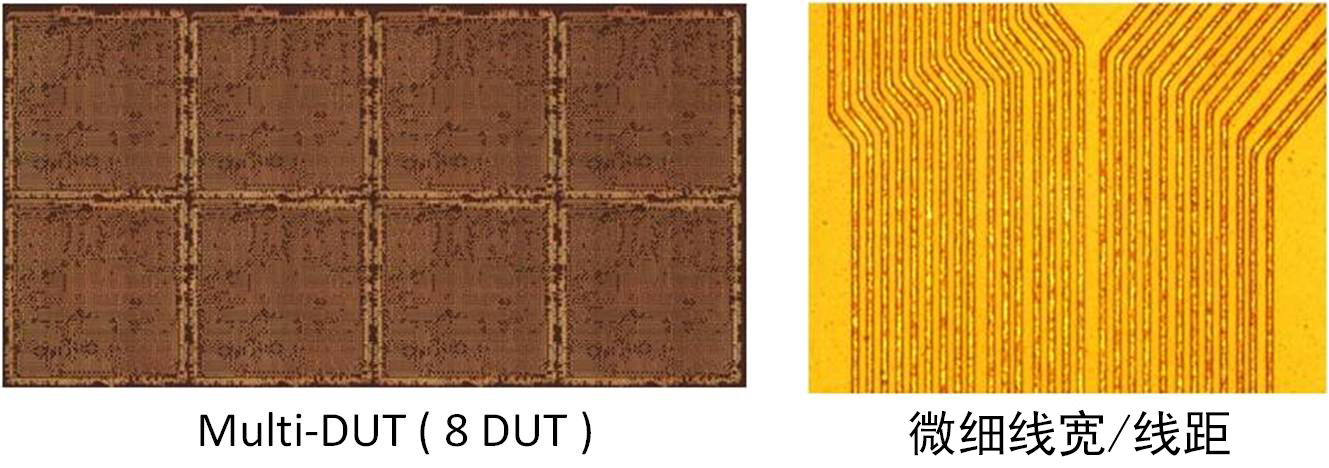

微细线宽/间距

经由L/S的微缩,将可提供更多的空间布线,除减少Layout的层数外,亦可提供Multi-DUT测试的设计,

加上信号传输的路径缩短,将有助於提升信号品质。晶测拥有Pitch 50um量产经验,除孔径设定为25um外,

L/S设定20um/20um,此测试方案已可对应到晶圆10nm制程等级的测试。